cache能够有效提升对存储器的访问速度,因此利用好这一组件,能够大大提升系统的整体性能,但是对cache的性能调优的第一步是如何量化对cache的访问性能。只有给出量化的方法,才能提出不同的策略,来改进策略。

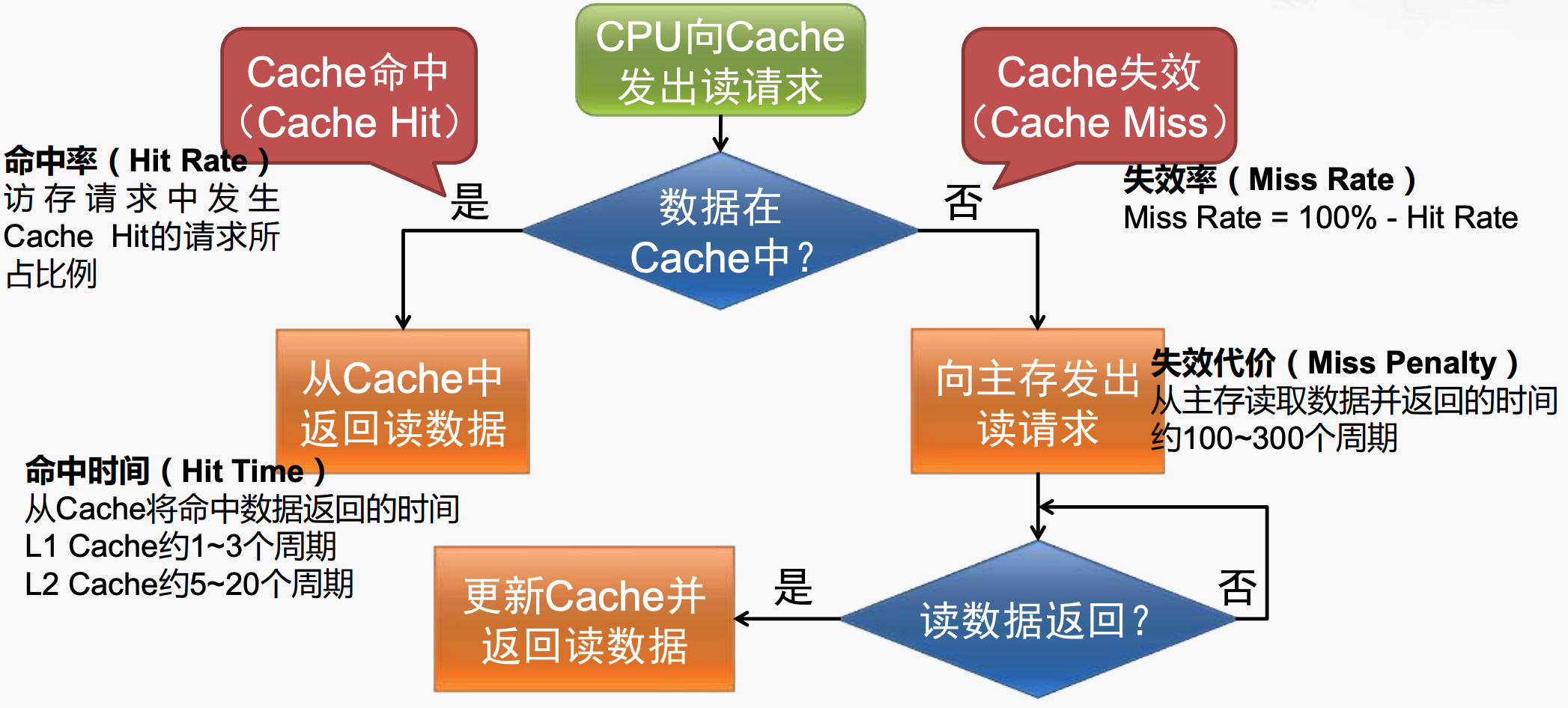

Review:Cache访问过程

4个性能指标:

hit rate: 访存请求中发生cache Hit的请求所占比例;hit time: 从cache将命中数据返回的时间;- L1 Cache约1~3个时钟周期;

- L2 Cache约5~20个时钟周期;

miss rate: 1 - hit rate;miss penalty: 从主存读取数据并返回的时间,约100~300个周期;

内存访问的时间衡量

在CPU运行过程中,CPU的时间可以具体分为两个部分:

- 真实执行具体指令花费的时钟周期;

- 等待内存系统花费的时钟周期;

这里将访问cache的时间算在了执行指令的时间中。

因此,得到如下计算公式:

$$

\text{CPU time = (CPU execution clock cycles + Memory-stall clock cycles)} \times \text{Clock cycle time}

$$

当CPU执行指令的时间越短,内存访问的瓶颈就越严重。

其中:

Memory-stall clock cycles主要是由于cache miss 导致,因此需要去读取main memory。而Memory-stall clock cycles又具体分为读和写两个部分:$$

\text{Memory-stall clock cycles = (Read-stall cycles + Write-stall cycles)}

$$Read-stall cycles可以进一步分解为以下形式:$$

\text{Read-stall cycles} = \frac{\text{Reads}}{\text{Program}} \times

\text{Read miss rate} \times

\text{Read miss pennalty}

$$简单来说,读操作造成的停顿时间,由指令中读操作的数量,这些读操作导致的miss rate,每个miss rate需要的miss penalty组成。

相比于读操作,写操作的过程更复杂,这个过程中涉及不同的策略。

当使用write through策略时,需要同时写入cache和memory。

这里有个疑问,之前提到在hit cache时才会有write through,但是这里还会发生miss,是不是与之前的冲突?这里我是这么理解的,对于write through的理解,以同时写到cache和memory为核心,至于写到cache是否miss,不是关注重点。

- 当hit cache时,写入cache的时间可以忽略,但是write buffer stalls,则是写入memory造成的。

- 当miss cache时,此时需要将main memory中的数据先读到cache中,然后再写。

综上所示,使用write through时的write-stall cycles如下:

$$

\text{write-stall cycles} = \frac{\text{Writes}}{\text{Program}} \times

\text{Write miss rate} \times

\text{Write miss pennalty} + \text{Write buffer stalls}

$$这里,因为memory处理写的速度超过CPU产生写操作的速度,因此

write buffer stalls可以忽略。综合来看,假设:

$$

\begin{align}

\text{write miss rate = read miss rate} \\

\text{write miss penalty = read miss penalty}

\end{align}

$$得到:

$$

\text{Memory-stall clock cycles} =

\frac{\text{Memory accesses}}{\text{Program}} \times

\text{Misses} \times

\text{Miss penalty}

$$进一步拆解得到:

$$

\text{Memory-stall clock cycles} =

\frac{\text{Instructions}}{\text{Program}} \times

\frac{\text{Misses}}{\text{Instructions}} \times

\text{Miss penalty}

$$当使用write back策略时,对于从cache中将数据写到memory也需要时间

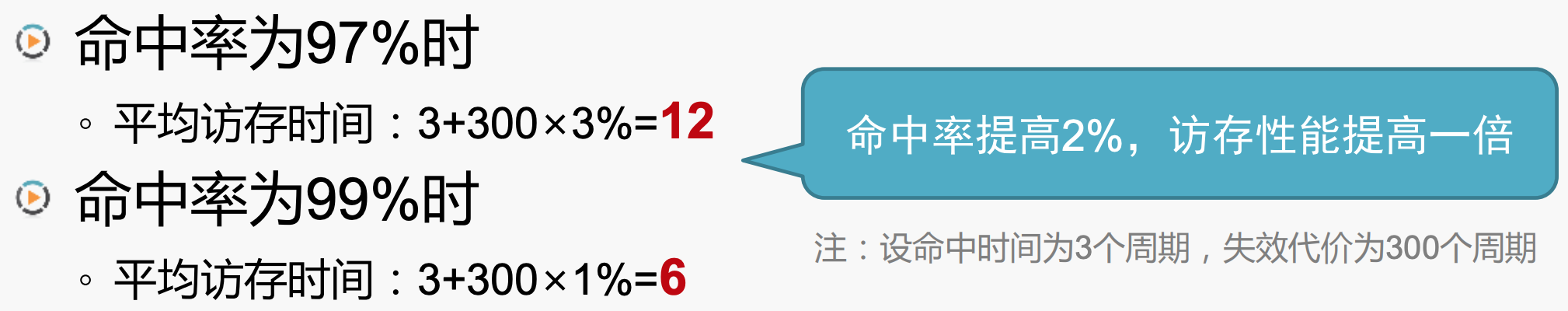

评价访存性能——平均访存时间

为了评价访问数据的性能表现,综合考虑hit和miss两种情况,人们想出了——平均访存时间,这个指标可以辅助cache性能的优化。

$$

\text{Average Memory Access Time} = \text{Hit Time} + \text{Miss Penalty} \times \text{Miss Rate}

$$

既然由3个因素决定,如果减少平均访存时间,就是分别减少这3项。

- 降低hit time 要求将cache做得小一些,结构不要太复杂。 但是小容量的cache容易失效,导致miss rate提升。

- 减少miss penalty 可以通过提高主存性能;或者在当前的cache和主存之间再增加一层cache。但是新增的cache也会遇到相同的问题。

- 减少miss rate 提升cache的容量,但是这样hit time就会增加,因此也不一定可行。

因此,这3个因素不是相互独立的,需要综合考虑才行。

实例分析

命中率提高了2%,但是平均访存时间提升了1倍,因此提升命中率带来的性能提升非常明显。