Multilevel cache

介绍

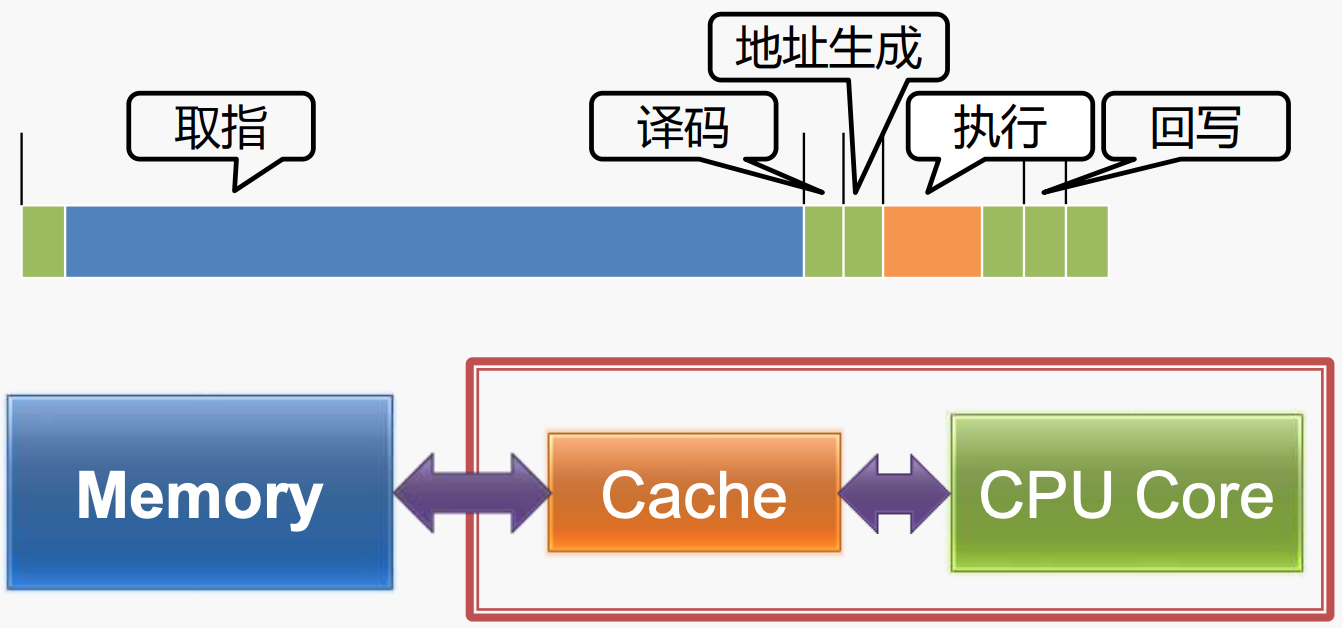

在内存系统中,为了弥补CPU访问内存的性能限制,采用了memory hierarchy的设计。同样的,在cache中,为了miss penalty,也可以采用这种策略——multilevel cache。

- 当第一层cache中发生了miss,第二层的cache就会被访问,这种大大减少了因对memory的访问造成的性能问题;

- 但所有的cache均出现miss时,才会访问main memory;

这种策略,同时考虑了成本和技术需求,在很多的问题上都是一样的思路。

设计考虑因素

对于一个层次化的cache结构,与设计单个cache使用的策略是很不同的。

- 对于第一层cache,着重解决减少hit time的问题; 一般来说,该层的cache容量,相比于单级的cache,都很小,比如block size很小;

- 第二层的cache着重解决减少miss penalty,以避免访问main memory; 第二层的cache则一般使用较大的cache size,比如设计较大的block size,以降低 miss rate,比如可以将set associative中每个set中cache lines的数量增加。

实例说明

80486的高速缓存

- 80486采用指令和数据共用的8KB Cache;

- 缺陷:指令和数据的局部性相互影响;

- 例如:一个数据密集的程序会很快占满Cache,几乎没有空间用于指令;

执行时间很短,取指时间很长,综合来看,并没有什么优势。

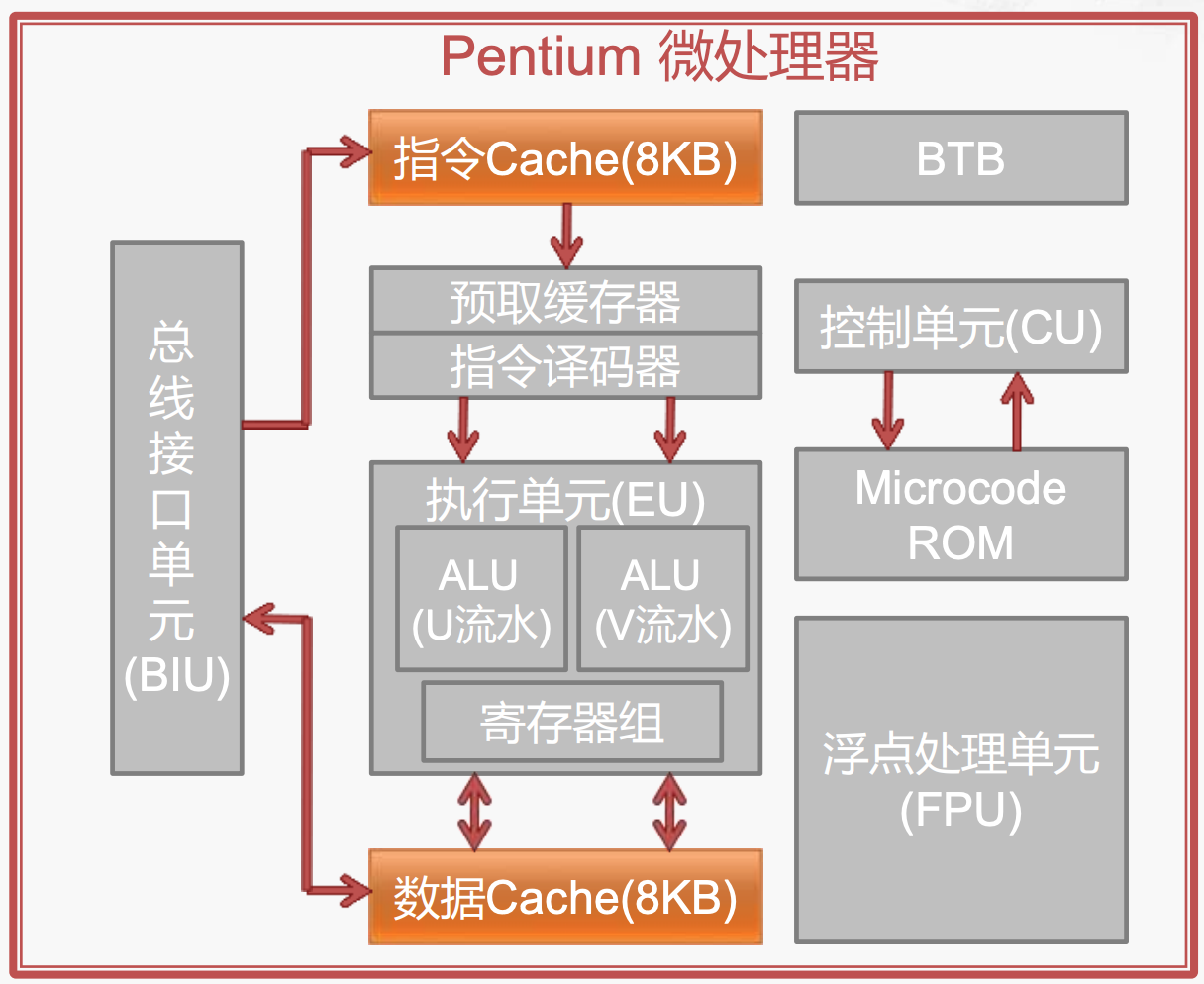

Pentium的高速缓存

- 将指令cache和数据cache分开,各自的局部性不会互相影响;

- 现代的L1 cache都会采用这种结构;

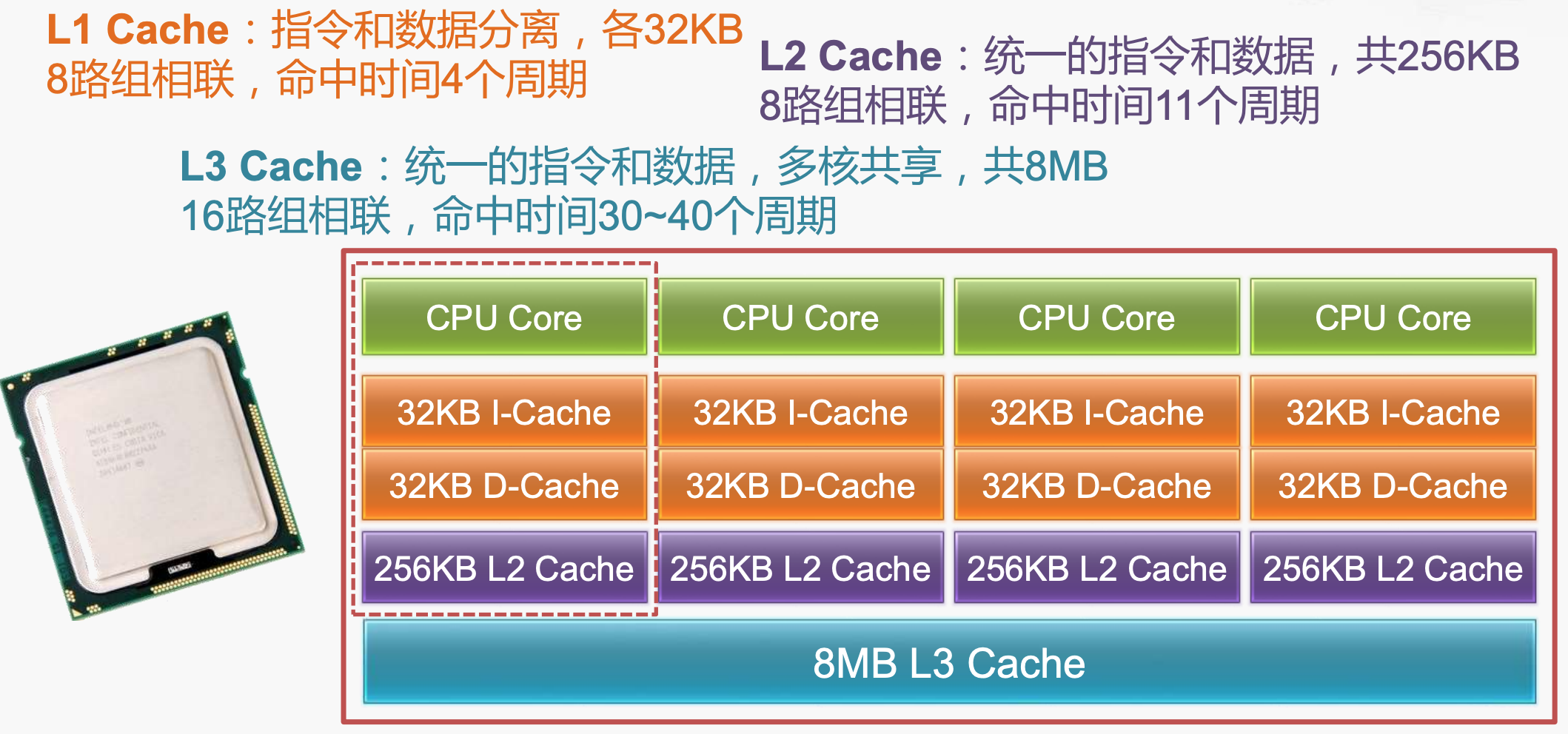

Core i7的多级高速缓存

- 现代的Cache结构均为多层的,并且从上到下,缓存的容量是递增的,即L1 cache是最小的,L3 cache最大。

- L1 cache做的最小,有成本的考量,也有multilevel caches设计思想在里边,L1 cache的主要目的在于减少cache的hit time,而做大后,则会增加hit time。

参考资料

- Computer Organization and Design - 5.4 - Reducing the miss Penalty Using Multilevel Caches

- 高速缓存的组织结构 - 第七讲 存储层次结构